行业首款基于台积电平台的光互连解决方案亮相 —— Alchip 与 Ayar Labs 展示面向下一代 AI 芯片的硅光子器件

在11月25日举行的 TSMC(台积电) 欧洲 OIP 论坛上,Alchip 和 Ayar Labs 联合展示了一款完全集成、在封装内的光学 I/O 引擎,该引擎基于 TSMC 的 COUPE 平台构建,可为下一代 AI 加速器提供光互连能力。这套解决方案将 Ayar Labs 的硅光子 TeraPHY 芯片、Alchip 的电接口芯片以及可插拔光纤连接器相结合,单颗加速器最高可提供 100 Tb/s 的带宽,并通过行业标准的 UCIe 接口与其他芯片连接。该方案主要面向那些需要光互连、但无法从零开始自行开发光学子系统的硬件开发商。

(图片来源:Tom's Hardware)

2024 年 TSMC 推出 Compact Universal Photonic Engine(COUPE)框架时,主要目标客户是 AMD、Nvidia 这类有能力自行设计电子集成电路(EIC)和光子集成电路(PIC)、并委托 TSMC 代工的大型芯片厂商。

然而,许多定制加速器设计公司并不具备像 Nvidia 那样的垂直整合能力(Nvidia 通过 NVL72、NVL144、NVL576 等平台掌控了从计算到扩展互连的完整技术栈),它们更倾向于尽可能授权现有技术,然后专注于开发能够形成差异化的 IP。这正是 Alchip 与 Ayar Labs 这套已量产就绪的光学子系统发挥作用的地方——它让规模较小的芯片设计公司能够相对轻松地为自家芯片添加光互连功能,而无需预先投入数千万美元。

Alchip 与 Ayar Labs 联合开发的这套解决方案是一个三芯片let 共封装光学 I/O 子系统,它由以下部分组成:

- 一颗 Alchip UCIe-A 转 UCIe-S 协议转换芯片let,用于终结加速器的 UCIe-A 接口,并在 UCIe-S(流式)上实现扩展协议(UALink、PCIe、Ethernet、SUE);

- 一颗 Alchip EIC,提供低功耗 SerDes、调制驱动、时钟和控制功能;

- 一颗 Ayar Labs TeraPHY PIC,采用硅光子技术完成光调制和光探测。

Alchip 的协议转换器还能够承载通过 UCIe 物理接口封装的非 UCIe 协议,因此可以兼容使用专有协议的计算 die。PIC 采用微环谐振器架构,配备可插拔光纤连接器以便于制造,并提供两种链路选项:PAM4 CWDM(单跳延迟 100–200 ns,BER < 10⁻⁶)和后续推出的 DWDM 版本(单跳延迟 20–30 ns,BER < 10⁻¹²)。

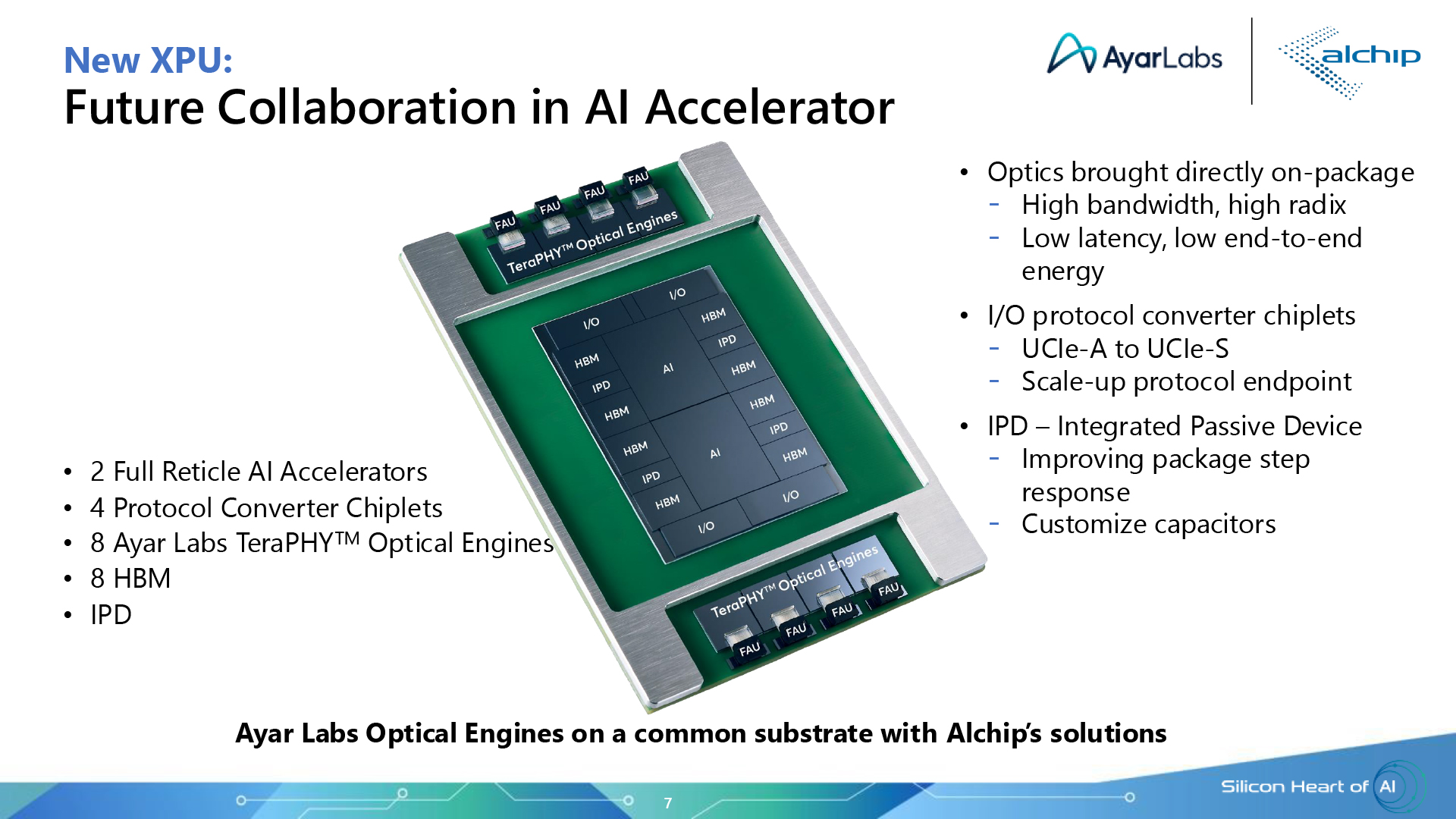

(图片来源:Alchip)

该光学子系统可实现极大规模扩展,单颗加速器支持 100+ Tb/s 带宽、256+ 个光端口,从而将跨多个机架的数百个处理器连接起来并作为单一巨型处理器运行。此外,两家公司还设想该方案可用于内存扩展器。

参考设计(实物模型)包含两颗满幅(full-reticle)加速器 die、八栈 HBM、四颗协议转换芯片let 和八个 Ayar Labs TeraPHY 光学引擎,所有部件都安装在同一块集成了无源器件(用于电源完整性)的基板上。Alchip 的系统图展示了该平台支持 XPU-to-XPU、XPU-to-switch、switch-to-switch 连接,甚至可以实现光学内存扩展。

- 收藏